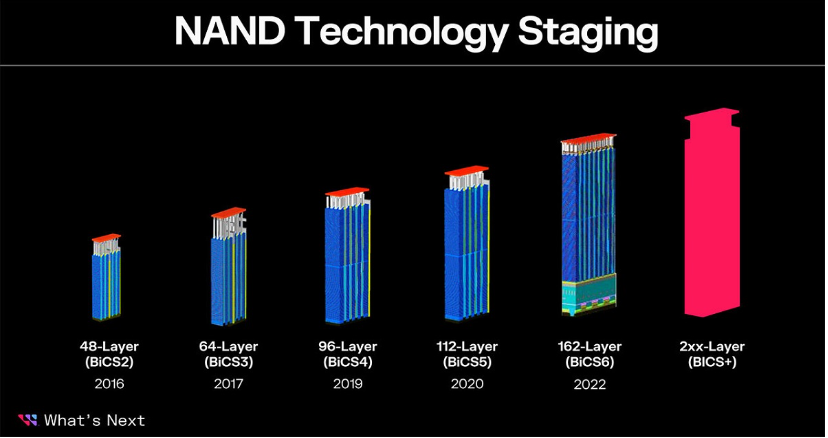

目前全球每天产生的数据量是非常庞大的,通过HDD和SSD存储在大容量的服务器和数据中心里,不过SSD在读/写速度、能耗和设备尺寸上都优于HDD,使得SSD正逐步取代HDD。SSD单位成本的扩展,其中一个原因归功于在存储单元上堆叠更多的层数。

据Xtech Nikkei报道,铠侠首席技术官Hidefumi Miyajima在东京城市大学举行的第71届应用物理学会春季会议上表示,计划到2031年开始批量生产超过1000层的3D NAND闪存芯片。

增加3D NAND器件中有源层的数量是目前提高闪存记录密度的最佳方法,因此所有3D NAND闪存制造商每1.5至2年就通过新的制程工艺节点来实现这一目标。不过每个新的制程工艺节点都会有一些挑战,由于3D NAND闪存需要在存储单元上堆叠更多层数,那么也要在横向和纵向上缩小存储单元,其中会采用新的材料,对于厂商研发上会有一定的难度。

目前铠侠最好的是去年推出的第8代BiCS 3D NAND闪存,为218层。为此铠侠和西部数据还开发了CBA(CMOS directly Bonded to Array)技术,将每个CMOS晶圆和单元阵列晶圆都是在其最优状态下单独制造的,然后粘合在一起,以提供增强的位密度和快速的NAND I/O接口速度。通过创新的横向收缩技术,将位密度提高了50%以上,NAND I/O接口速度超过了3.2Gb/s,比上一代产品提高了60%。

铠侠应该会沿用目前的工艺技术路线,开发1000层的3D NAND闪存芯片。